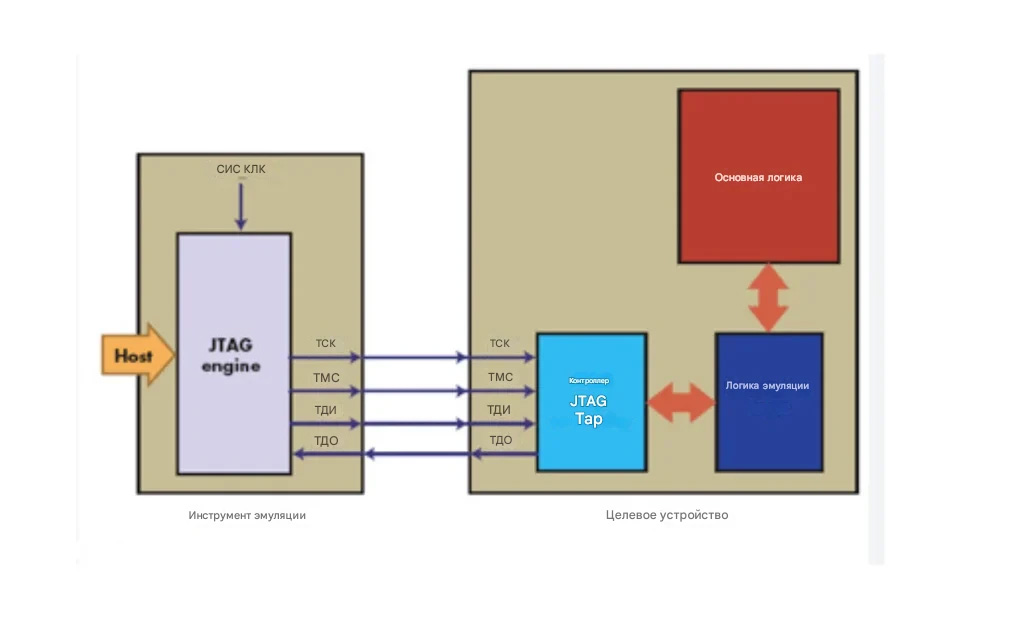

Современные электронные устройства становятся всё компактнее, а их схемы — всё сложнее. В таких условиях физический доступ к внутренним узлам платы для тестирования и отладки часто невозможен: места для пробников или тестовых разъёмов просто не остаётся. Именно здесь на помощь приходит JTAG (Joint Test Action Group) — стандартизированный интерфейс для программирования, отладки и тестирования цифровых схем с минимальным физическим доступом.

Однако даже при наличии JTAG-интерфейса разработчики нередко сталкиваются с проблемами подключения к целевым устройствам — будь то микроконтроллер, процессор или FPGA. В этой статье мы рассмотрим наиболее распространённые причины сбоев JTAG-соединения, способы их устранения и ключевые факторы, которые следует учитывать при выборе отладочного оборудования.

Типичные проблемы подключения JTAG и их решения

Некорректная конфигурация JTAG программатора

Если среда разработки (например, Code Composer Studio, Visual Studio, IAR или Vivado) не распознаёт целевое устройство, первым делом проверьте настройки JTAG.

Возможные причины:- Неправильно выбрана модель JTAG-пробника (например, XDS100 вместо XDS200 для устройств Spectrum Digital).

- Отсутствует поддержка целевого чипа в используемом ПО.

- Проверьте файл конфигурации цели (Target Configuration File) на соответствие типу устройства и пробника.

- Внимательно изучите даташит на SoM модуль, микроконтроллер или FPGA.

- Используйте встроенную функцию «Test Connection» для проверки работоспособности соединения.

Неисправные соединения JTAG-пинов

Возможные причины:

- Ослабленный или неправильно установленный JTAG-разъём на плате.

- Перепутанные или неподключённые сигнальные линии (TDI, TDO, TCK, TMS, nTRST).

- Повреждённый кабель JTAG.

- Неисправный USB-порт на ПК или использование «зарядного» USB-кабеля без линий данных.

- Повреждение дорожек на печатной плате.

- Визуально и с помощью мультиметра проверьте целостность кабеля и разъёмов.

- Убедитесь, что JTAG-коннектор плотно установлен на плате.

- Сверьте разводку JTAG-сигналов со схемой платы.

- Подключите JTAG-адаптер к другому USB-порту компьютера.

- Закладывайте проверку JTAG-соединений уже на этапе проектирования и трассировки платы.

Несовместимость напряжений и проблемы с питанием

Возможные причины:

- JTAG работает на 3.3 В, а целевое устройство — на 1.8 В (или наоборот).

- Нестабильный или шумный источник питания.

- Отсутствие питания на целевом устройстве.

- Сверьтесь с даташитом: убедитесь, что уровни напряжений совместимы.

- При несовпадении используйте преобразователь уровней (level shifter).

- Выбирайте JTAG-адаптеры с автоматическим определением напряжения или поддержкой широкого диапазона (1.2–5 В).

- Используйте качественный стабилизированный блок питания с прошедшей проверку надёжностью.

- Добавьте на плату фильтрующие конденсаторы, LDO-стабилизаторы и защиту от перенапряжений.

Проблемы с сигналом сброса (Reset)

Возможные причины:

- Сигнал RESET не доходит до чипа.

- Устройство «застревает» в состоянии сброса.

- Встроенный код в Flash постоянно генерирует сброс (например, из-за ошибки в прошивке).

- Проверьте целостность и форму сигнала RESET с помощью осциллографа.

- Убедитесь, что сброс не блокируется внешними компонентами (например, подтяжками).

- Для устройств с Flash: переведите в режим загрузки (boot mode) или выполните полную очистку памяти.

Несовпадение тактовой частоты и нестабильность тактового сигнала

Возможные причины:

- Тактовая частота JTAG превышает допустимую для целевого устройства.

- Тактовый сигнал не подключён или имеет сильные искажения (джиттер, перекосы).

- Используется фиксированный такт, хотя устройство требует адаптивного.

- Установите тактовую частоту в соответствии с рекомендациями из даташита (часто 1–10 МГц).

- Убедитесь, что линия TCK правильно разведена на плате.

- Минимизируйте длину тактовой дорожки и избегайте прокладки рядом с шумными цепями.

- Используйте буфер тактового сигнала для длинных трасс.

- Проверьте целостность сигнала: он должен быть чётким, без звонов и искажений.

Плохая целостность сигнала (Signal Integrity)

Возможные причины:

- Длина JTAG-кабеля превышает 50 см.

- Отсутствует согласование импеданса.

- Нет экранирования сигнальных линий.

- Плохая разводка на плате (длинные, параллельные дорожки).

- Сократите длину JTAG-кабеля и сигнальных трасс на плате.

- Применяйте согласующие резисторы на концах линий.

- Используйте экранированные витые пары для внешних соединений.

- Добавьте буферы или повторители сигналов при необходимости.

- Для кабелей >50 см — устанавливайте развязывающие конденсаторы на каждую сигнальную линию.

Электромагнитные помехи (EMI)

Решение:

- Обеспечьте качественное заземление платы и корпуса.

- Используйте экранированные кабели и металлические разъёмы.

- Отключите соседние интерфейсы (USB, Ethernet, Wi-Fi), которые могут создавать помехи.

- Разместите JTAG-цепи подальше от импульсных преобразователей и высокочастотных модулей.

- При необходимости — примените повторители сигнала для компенсации потерь.

Ошибки в разводке печатной платы (PCB Layout)

Рекомендации по проектированию:

- Используйте сплошную земляную плоскость для снижения шума.

- Размещайте развязывающие конденсаторы как можно ближе к питанию FPGA/МК.

- Минимизируйте длину JTAG-трасс.

- Избегайте острых углов и параллельных участков сигнальных линий.

- Обеспечьте согласование импеданса и при необходимости — терминирование линий.

Заключение

Устранение типичных проблем подключения — от несовместимости напряжений до плохой целостности сигнала — позволяет значительно сократить время отладки и избежать дорогостоящих переделок на этапе производства. Инвестируйте в качественные JTAG-адаптеры, следуйте best practices при проектировании и всегда сверяйтесь с документацией производителя — и ваша отладка станет быстрой, надёжной и предсказуемой.